2015/12/25

apt-get install iverilog gtkwave

/*2入力ANDゲート p133*/ module AND(A,B,F); input A,B; output F; assign F=A&B; endmodule

/*2入力ANDゲート(and2.v)テストベンチ p135*/

/*時刻単位を1ナノ秒に変更 デフォルトは秒*/

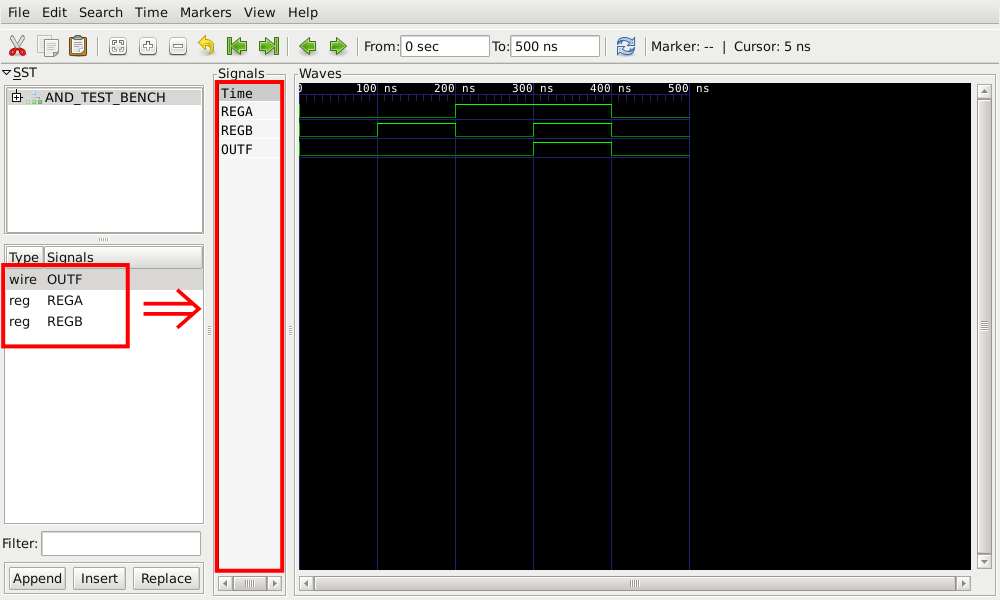

`timescale 1ns/1ns

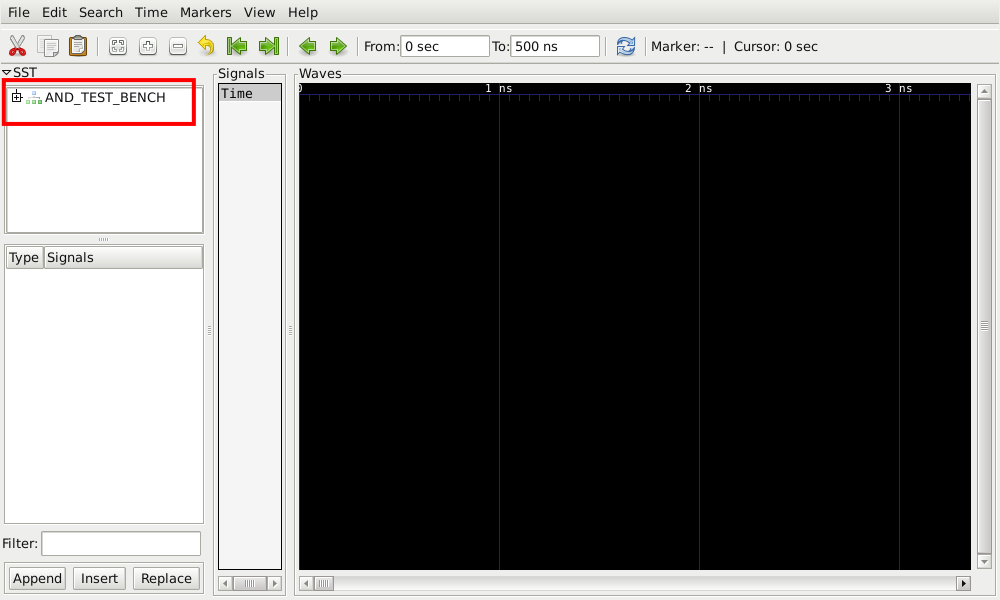

module AND_TEST_BENCH;

reg REGA,REGB;

wire OUTF;

AND ANDTB(REGA,REGB,OUTF);

initial begin

$dumpfile ("tmp.vcd"); //出力ファイル GTKwaveで波形表示するために一時的に作成

$dumpvars(0, AND_TEST_BENCH); //タイミングチャートとして出力するモジュール

$monitor ($stime, "A=%b B=%b F=%b",REGA,REGB,OUTF); //タイミングチャートとして出力するもの

REGA=0; REGB=0;

#100 REGB=1;

#100 REGA=1;REGB=0;

#100 REGB=1;

#100 REGA=0;REGB=0;

#100 $finish;

end

endmodule

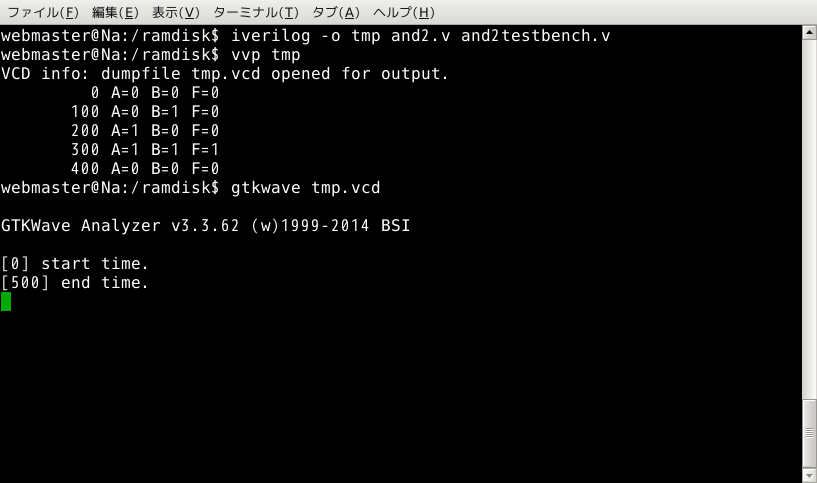

iverilog -o tmp and2.v and2testbench.v vvp tmp gtkwave tmp.vcdvvpを実行する。時刻(100nsごと),A,B,Fのセットで実行結果を表示する。